# ASIC/Merchant Chip-Based Flash Controllers

Dr. Jeff Yang

Principal Engineer

Storage Research Dept.

Silicon Motion, Inc.

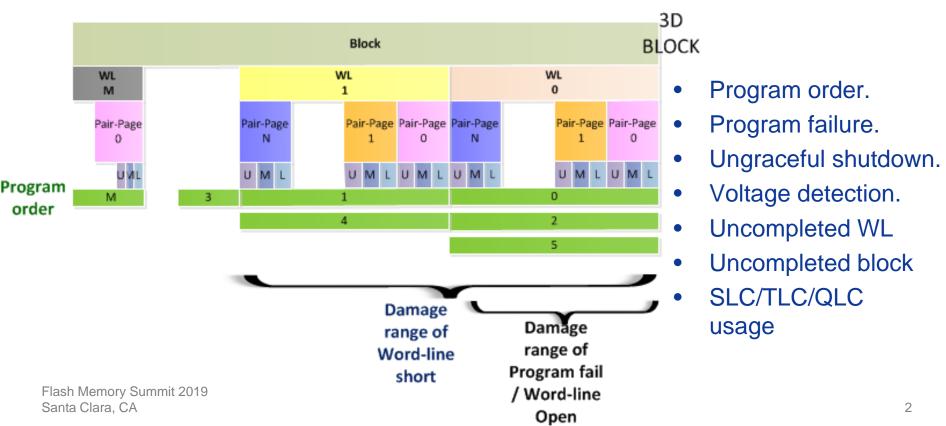

# NAND usage/failure/defect

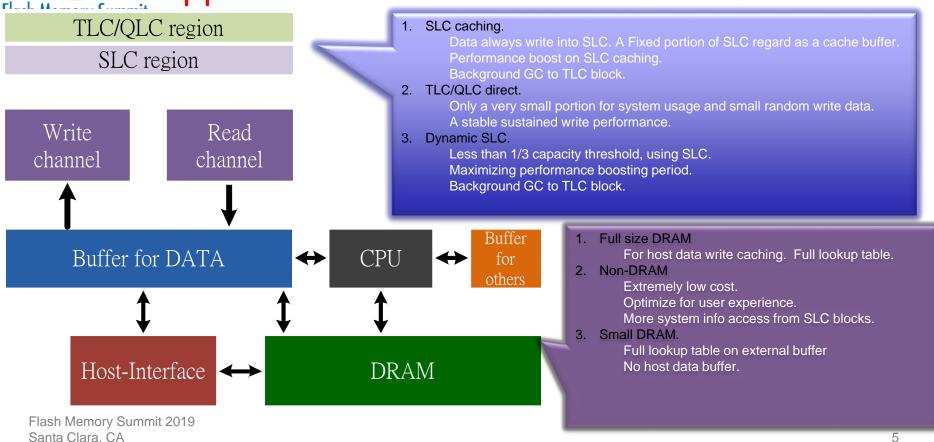

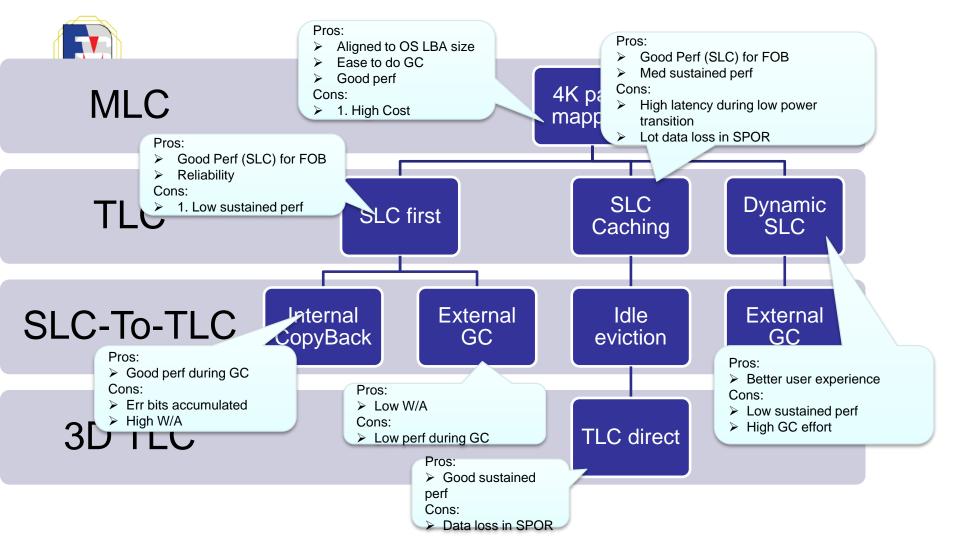

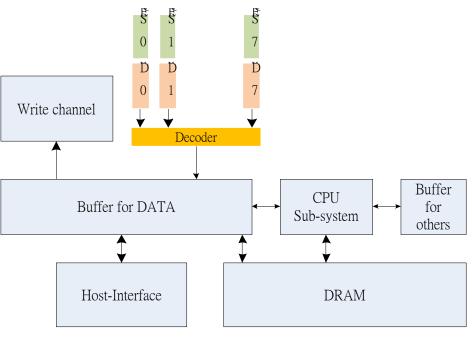

# Basic Architecture of SSD controller

TLC/QLC region SLC region Write Read channel channel Buffer Buffer for DATA CPU  $\leftrightarrow$ others Host-Interface DRAM

## Different TLC/QLC reliability issue Flash M TLC/QLC region 1. 3D. TLC/QLC One-pass program, two-pass program, multi-pass program. SLC region 2. Program failure protection flow. Program failure range. Read back data from flash cache buffer. DRAM back up. SLC back up, SRAM backup. 3. One WL open and Multi-WL short. Write Read Need raid or read back check after program. 4. TLC/SLC dynamic changing usage. channel channel TLC endurance calculation issue. 5. Internal copy back for SLC to TLC Internal read without ECC correction Buffer Buffer for DATA **CPU** others

DRAM

Host-Interface

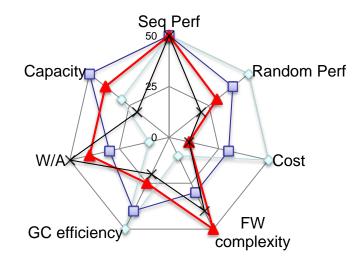

## Application combinations on TLC/QLC

# Challenge: Support all combinations

and cost efficiency

# 3D TLC/QLC

One-pass

Two-pass

Multi-pass

# SLC usage

SLC caching

**TLC** direct

SLC/(TLC/QLC) dynamic

# External buffer

Full DRAM

Non-DRAM

Partial DRAM

DRAM/ DRAM-less/ Small DRAM SLC-first/ TLC-direct write/ Dynamic SLC One-pass /

Multi-pass/

Pair-page

mapping

WL to WL short Failure range

# All the issues combine together

Capacity (RAID overhead) Binary/arbitrary Program failure DRAM-backup/ Flash-cache/ RAID recover/ WL open Failure range

Recovery latency

on

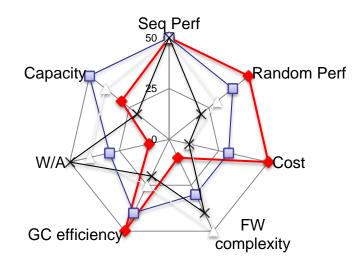

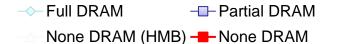

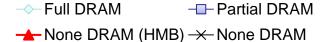

## Full DRAM Pros High Perf GC efficiency Low W/A Low complexity Cons · Capacity limitation DRAM bandwidth limitation Power consumption Cost

## **Partial DRAM** Pros GC efficiency Capacity limited by L2P address bit (8TB) Cons Med Random Perf (DRAM L2P buffer) Med W/A

## Full DRAM

#### Pros

- High Perf

- GC efficiency

- Low W/A

- Low complexity

#### Cons

- Capacity limitation (2TB)

- DRAM bandwidth limitation

- Power consumptionCost

# Partial DRAM

#### Pros

- GC efficiency

- Capacity limited by L2P address bit (8TB)

#### Cons

- Med Random Perf (DRAM L2P buffer)

- Med W/A

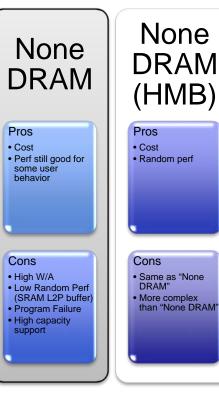

## None DRAM

## Pros

- Cost

- Perf still good for some user behavior

#### Cons

- High W/A

- Low Random Perf (SRAM L2P buffer)

- Program Failure

- High capacity support

## None DRAM (HMB)

## Pros

- Cost

- Random perf

### Cons

- Same as "None DRAM"

- More complex than "None DRAM"

## Full DRAM

#### Pros

- High Perf

- GC efficiency

- Low W/A

- Low complexity

#### Cons

- Capacity limitation (2TB)

- DRAM bandwidth limitation

- Power consumption

- Cost

# Partial DRAM

## Pros

- GC efficiency

- Capacity limited by L2P address bit (8TB)

#### Cons

- Med Random Perf (DRAM L2P buffer)

- Med W/A

## None DRAM

### Pros

- Cost

- Perf still good for some user behavior

#### Cons

- High W/A

- Low Random Perf (SRAM L2P buffer)

- Program Failure

- High capacity support

## None DRAM (HMB)

## Pros

- Cost

- Random perf

#### Cons

- Same as "None DRAM"

- More complex than "None DRAM"

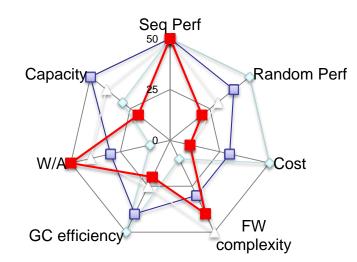

## Full DRAM

#### Pros

- High Perf

- GC efficiency

- Low W/A

- Low complexity

#### Cons

- Capacity limitation (2TB)

- DRAM bandwidth limitation

- Power consumption

- Cost

# Partial DRAM

### Pros

- GC efficiency

- Capacity limited by L2P address bit (8TB)

#### Cons

- Med Random Perf (DRAM L2P buffer)

- Med W/A

## None DRAM

## Pros

- Cost

- Perf still good for some user behavior

#### Cons

- High W/A

- Low Random Perf (SRAM L2P buffer)

- Program Failure

- High capacity support

## None DRAM (HMB)

## Pros

- Cost

- Random perf

#### Cons

- Same as "None DRAM"

- More complex than "None DRAM"

# Enhanced reliability on SSD controller

- ECC to NAND E2E

- Stronger LDPC engine.

Increase to 4KB LDPC.

- SRAM-ECC.

- DRAM-ECC.

- Host interface E2E

# Flash Memory Su

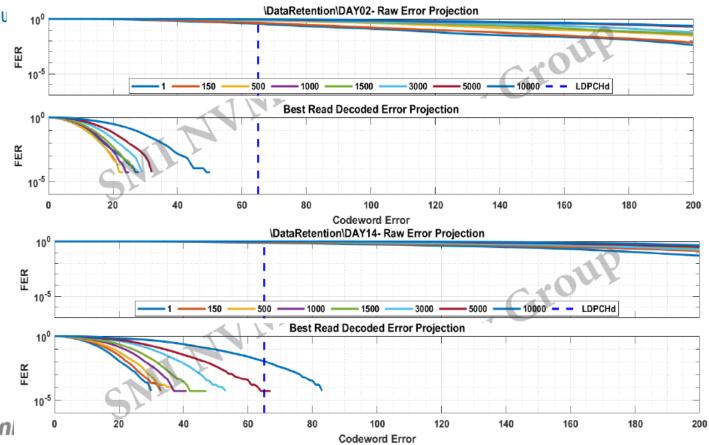

## Low temp data retention

## Low temp data retention issue.

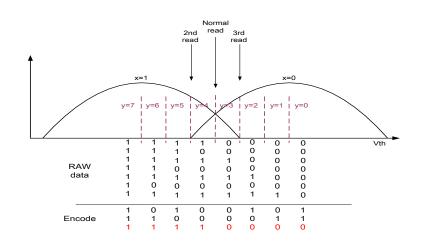

## Soft-information interface

- In order to provide better decoder's correction capability, using the soft-info to get more reliability bits.

- NAND interface support .

- Traditional read/retry interface.

- Direct soft-info interface.

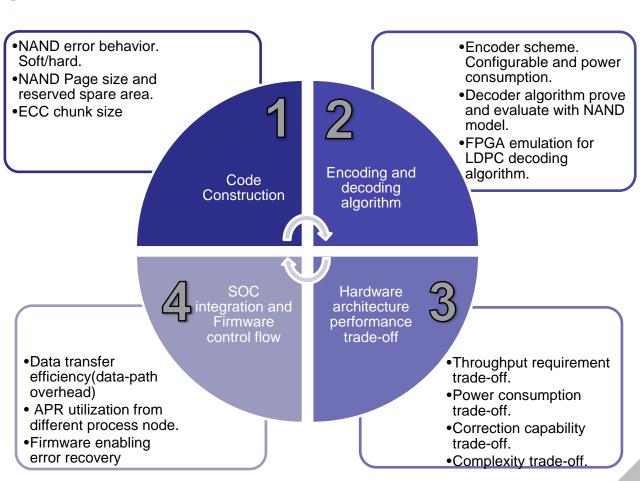

## ECC design loop related to NAND characteristics.

## Flash Memory Summit

- Keep improving the LDPC performance.

- For higher throughput 8~16GB/sec, we may go back to step1.

- After 16nm process, the design iteration depth will from codeconstruction to trial APR.

- EX: Find the Routing congestion issue in step 4, it may need to solve from step1.

- 12nm process is another new story on the LDPC engine design

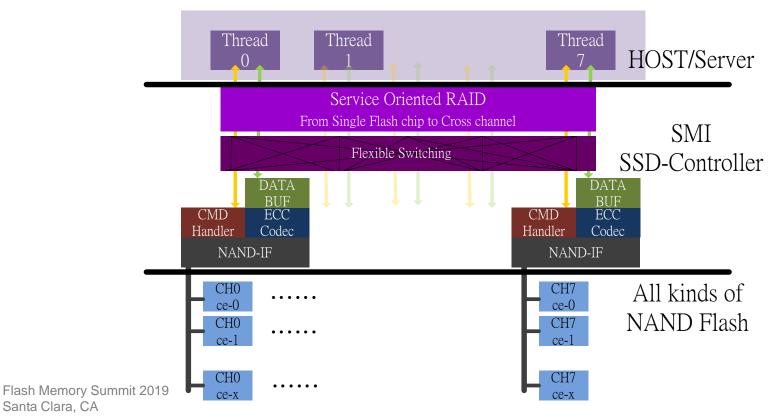

## 12nm process impact the and SOC design

- SRAM power consumption and the routing congestion.

- Single NAND channel will have higher than 1.2GB/sec throughput.

- 4-channel for Client SSD, 8-channel for enterprise and 16-channel for Data-center.

- Latency consistency. Decoding latency may blockage the chunk decoding between channels.

- Program suspend for read.

- Erase suspend for read.

- Controller buffer management for the read/write mixed behavior.

Santa Clara, CA

## Thread → buffer → NAND

19

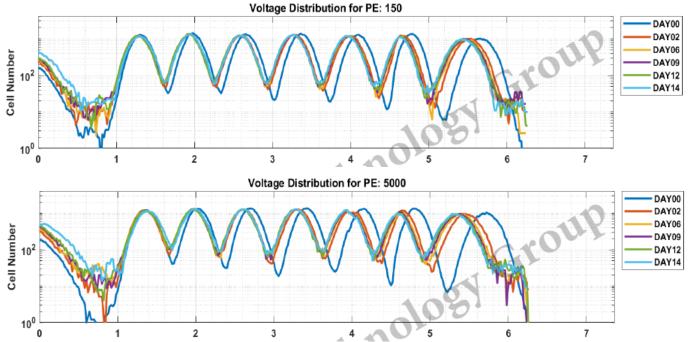

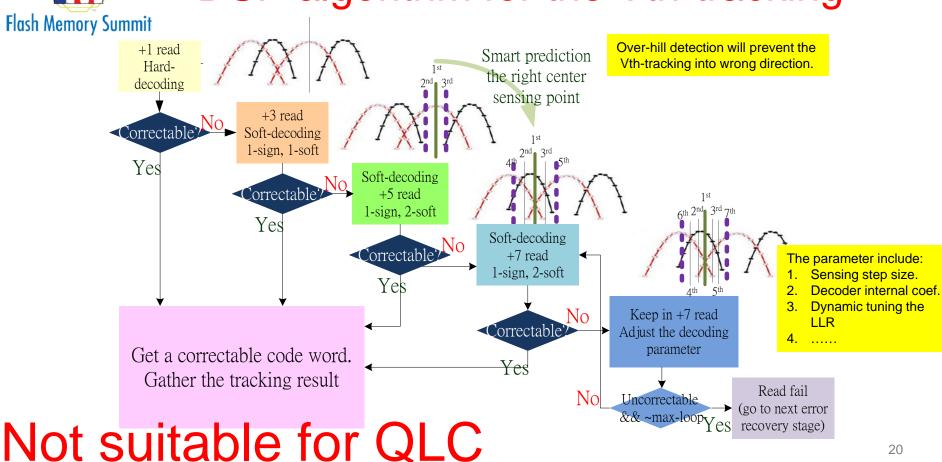

# DSP algorithm for the Vth-tracking

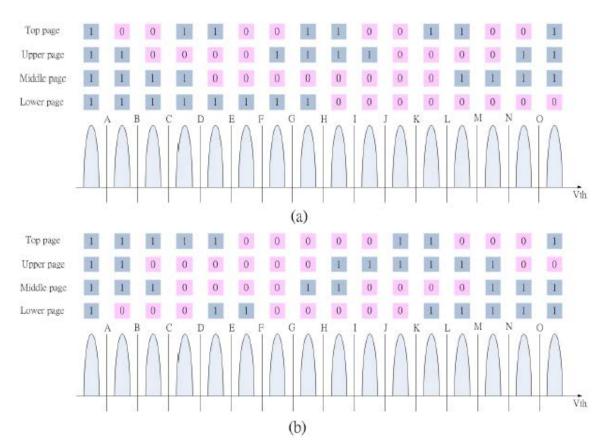

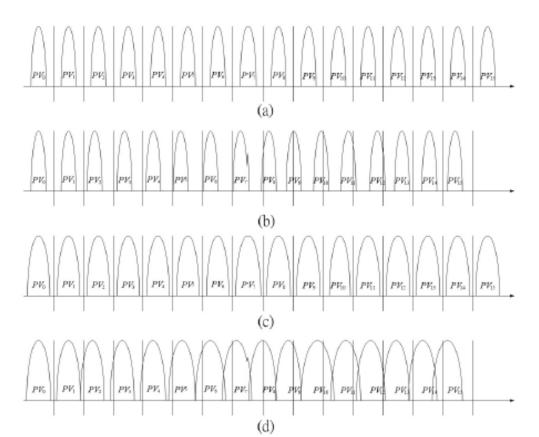

# QLC gray mapping

# Vth distribution shifting case

Traditional Vthtracking is not efficient.

# Controller design future

- Host based or Device based FTL.

- Multi-tenant, guarantee service, latency.

- Always need stronger ECC engine, especially for the hard-info only decoding.

- One sign-bit and one soft-bit still need higher decoding efficiency.

- Advanced process is expensive, single controller should cover three NAND generations

# Thanks for your attention!

Visit our booth #413 for more information