#### MRAM based NVME SSD Architecture

Lloyd Liu, R&D director

Sage-Micro Corporation

Hangzhou Dianzi university (HDU), PHD candidate

## 1, Why MRAM for SSD?

2, How MRAM implement on NVME SSD

#### What's MRAM?

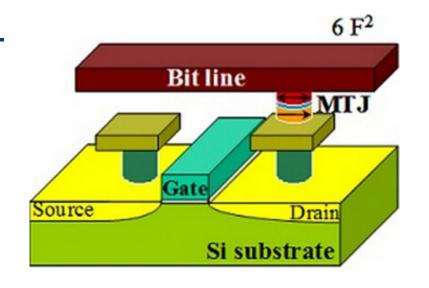

Magnetoresistive randomaccess memory (MRAM) is a type of non-volatile random-access memory which stores data in magnetic domains.

#### How MRAM works?

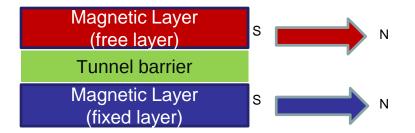

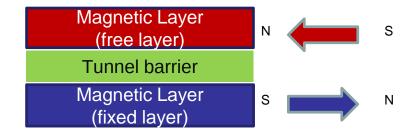

The state of the bit is detected as a change in resistance. Low resistance as logic 0 while high resistance as logic 1

Magnetic vectors are parallel low resistance. "0"

Magnetic vectors are anti-parallel high resistance. "1"

#### The feature of MRAM

- Non-volatile medium;

- Ultra high read/write speed;

- infinitely accessed times.

# Memory compare

| O.                                | SRAM                     | eDRAM                                            | DRAM                                             | eFLASH<br>(NOR)       | FlASH<br>(NAND)                  | FRAM                      | PRAM                             | MRAM               | RRAM                             |

|-----------------------------------|--------------------------|--------------------------------------------------|--------------------------------------------------|-----------------------|----------------------------------|---------------------------|----------------------------------|--------------------|----------------------------------|

| Endurance<br>(cycles)             | Unlimited                | Unlimited                                        | Unlimited                                        | 105                   | 105                              | 1014                      | 109                              | Unlimited          | 109                              |

| Read/write<br>access time<br>(ns) | <1                       | 1–2                                              | 30                                               | 10/10 <sup>3</sup>    | 100/106                          | 30                        | 10/100                           | 2–30               | 1–100                            |

| Density                           | Low (six<br>transistors) | Medium                                           | Medium                                           | Medium                | High (multiple<br>bits per cell) | Low (limited scalability) | High (multiple<br>bits per cell) | Medium             | High (multiple<br>bits per cell) |

| Write power                       | Medium                   | Medium                                           | Medium                                           | High                  | High                             | Medium                    | Medium                           | Medium             | Medium                           |

| Standby power                     | High                     | Medium                                           | Medium                                           | Low                   | Low                              | Low                       | Low                              | Low                | Low                              |

| Other                             | Volatile                 | Volatile.<br>Refresh power<br>and time<br>needed | Volatile.<br>Refresh power<br>and time<br>needed | High voltage required | High voltage<br>required         | Destructive readout       | Operating T < 125 °C             | Low read<br>signal | Complex<br>mechanism             |

Flash Memory Summit 2019 Santa Clara, CA

# Disadvantage

### 1, Expensive

2, temperature endurance

3, not standardization

#### MRAM Vendors

#### MRAM memory

- ✓ Everspin Technologies

- ✓ Avalanche Technology

- Crocus Nanoelectronics

#### **Embedded MRAM Technologies**

- ✓ Intel

- ✓ Samsung

Everspin has completed development activity and entered the pilot production phase of its 28 nm 1-Gigabit (Gb) Spin Torque Transfer Magnetoresistive Random Access Memory (STT-MRAM) product.

# **Everspin MRAM features**

- 1. 1Gb density

- 2. JEDEC-like DDRx interface with specific modifications

- 3. High bandwidth (1333 MT/s per pin) with true byte addressability and extremely low latency

- 4. x8, x16 data width Configuration

- 5. high endurance

# The SSD challenging?

#### NVMe SSD with feature of:

- 1. faster to access data

- 2. Low latency

- 3. higher Input/Output Operations (IOPS)

But with the increase of capacity and speed:

Power failure problems become challenging

## 1, Why MRAM for SSD?

2, How MRAM work on NVME SSD

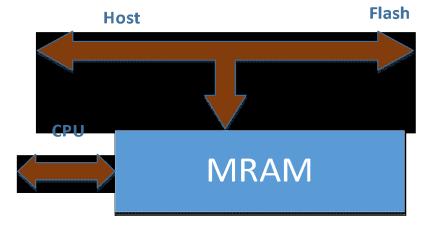

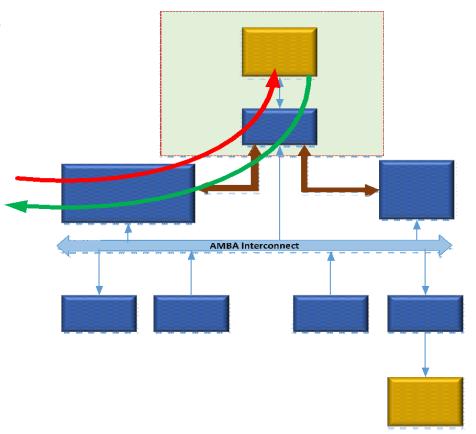

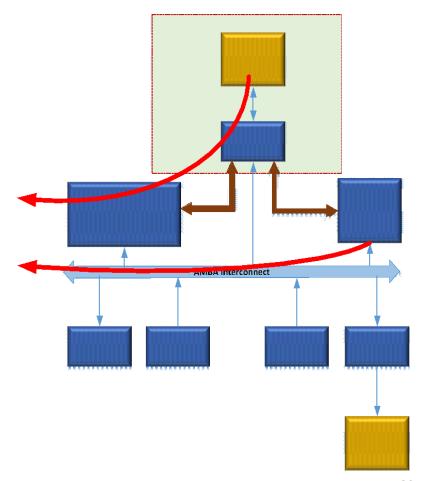

# MRAM Application option (1/3)

1, MRAM Store mapping table only

Bandwidth required is low

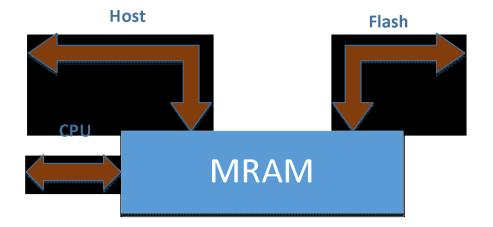

## MRAM Application option (2/3)

2, Table & Data backup

Store mapping table and backup data only.

Bandwidth required is medium

# MRAM Application option (3/3)

3, Table & Data cache

Store mapping table, and MRAM work as cache

Bandwidth required is high

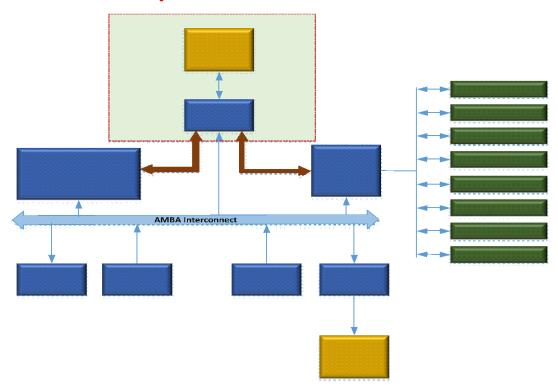

# A New SSD Architecture with the everspin MRAM chip

- NVME CONTROLLER

- 2. FLASH CONTROLLER(16)

- NVME CPU

- 4. FTL CPU

- 5. DRAM CONTROLLER

- 6. MRAM CONTROLLER

- 7. Peripher

### **MRAM** distribution

Permanent Mappping Table

Three usage of MRAM

1. Permanent FTL table

2

**Data Cache**

2. Nyme Data Cache

3. Hot data mirror buffer

3

Hot User Data

#### PCIE Gen3x4 bandwidth

PCIE GEN3 8Gb (130~128) \*4 ≈ 4GB.

DRAM with 80% Utilization to Support R/W,

required 10GB

DDR1333 \* 64 bit Required ≈1.3G\*8 (10.4GB)

How about Gen4\*4 ?

DDR2666\*64

#### Feature of SSD with MRAM

- Power loss data integrity, No super-cap

- FTL concise and robust, few data need protect when power loss.

- ultra low write latency

- ultra low read latency when user data cache hit

Write Latency

Response immediately when data push to MRAM

# Read Latency

Read Data0, Cache hit include nvme data or hot mirror data.

# Ultra low read latency

## Summary

- 1, MRAM is infinitely accessed and Non-volatile memory.

- 2, The NVME SSD With MRAM improved performance of power failure, and read/write latency.

# Thank you!