## NRAM Carbon Nanotube Memory

Bill Gervasi Principal Systems Architect bilge@Nantero.com

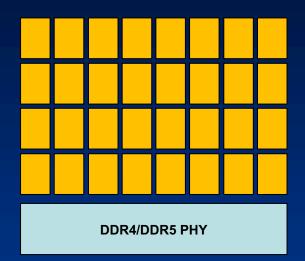

DDR4 DDR5

.....

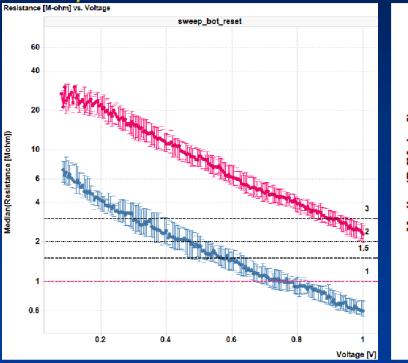

Nantero NRAM is a persistent memory using carbon nanotubes to build resistive arrays which can be arranged in a DRAM compatible device or deposited directly on circuits

Embedded

**HBM**

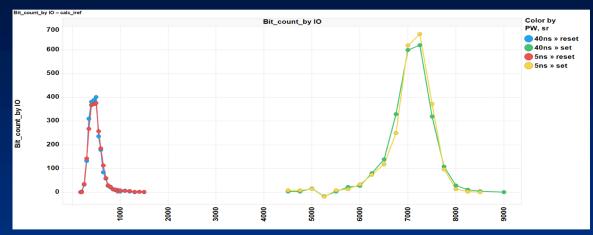

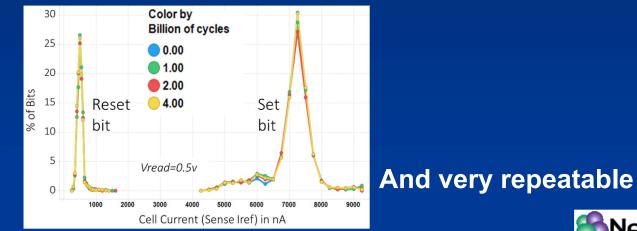

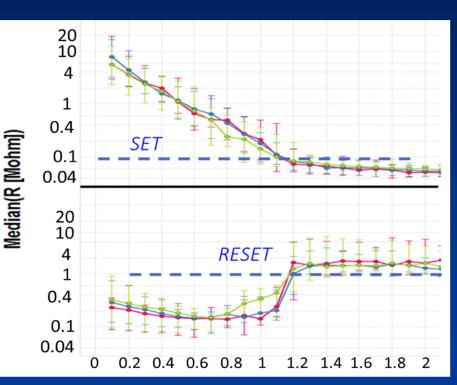

#### Consistent operation from 40 ns down to 5 ns read/write per cell

Voltag

е

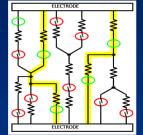

NRAM crosspoint tiles fit into the DDR protocol at full DRAM speed

No isolation selector diode/transistor needed

Santa Clara, CA August 2019

5

TERO

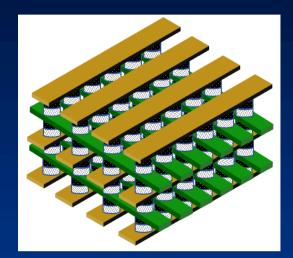

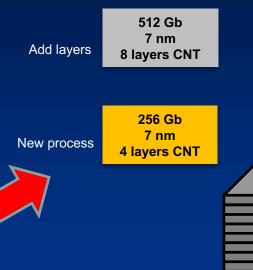

### NVRAM scales much better than DRAM

Add layers

New process

128 Gb

14 nm

8 layers CNT

64 Gb 14 nm

**4 layers CNT**

16 Gb 28 nm 4 layers CNT

#### Expect up to 512 Gb/die = 2 TB/package in DDR5 market window

16-die stacks

Santa Clara, CA August 2019

NTERO

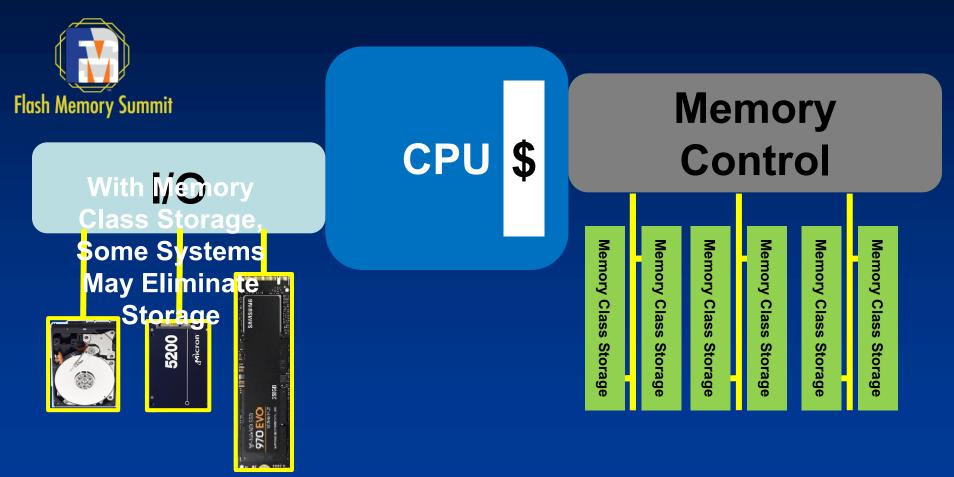

One step closer to the Holy Grail of end to end...

# **Data Persistence**

Registers

Cache

√ Memory Class Storage

NRAM

NVDIMM  $\sqrt{SSD}$   $\sqrt{Mag}$ Optane  $\sqrt{NVMe}$   $\sqrt{Hard Drive}$

## Thank you

## Bill Gervasi Principal Systems Architect bilge@Nantero.com